Не считая параллельного соединения триггеров для построения регистров употребляются последовательное соединение этих элементов.

Последовательный регистр (регистр сдвига) в большинстве случаев помогает для преобразования последовательного кода в параллельный и напротив. Использование последовательного кода связано с необходимостью передачи громадного количества бинарной информации по ограниченному количеству соединительных линий. При параллельной передаче разрядов требуется много соединительных проводников. В случае, если бинарные разряды последовательно бит за битом передавать по одному проводнику, то возможно существенно сократить размеры соединительных линий на плате (и размеры корпусов микросхем).

Принципиальная схема последовательного регистра, собранного на базе D?триггеров и разрешающего осуществить преобразование последовательного кода в параллельный, приведена на рисунке 3.

Рисунок 3. Схема последовательного регистра.

В этом регистре триггеры соединены последовательно, другими словами выход первого соединён с входом второго и т.д. Условно-графическое изображение рассмотренного последовательного регистра приведено на рисунке 4.

Рисунок 4. Обозначение последовательного регистра на принципиальных схемах.

Входы синхронизации в последовательных регистрах, как и в параллельных, объединяются. Это снабжает одновременность смены состояния всех триггеров, входящих в состав последовательного регистра.

Преобразование последовательного кода в параллельный производится следующим образом. Отдельные биты бинарной информации последовательно подаются на вход D0. Любой бит сопровождается отдельным тактовым импульсом, что поступает на вход синхронизации C.

По окончании поступления первого тактового импульса логический уровень, присутствующий на входе D0, запоминается в первом триггере и поступает на его выход, а так как он соединён с входом второго триггера, то и на его вход.

По окончании поступления второго тактового импульса логический уровень, присутствующий на входе второго триггера, запоминается в нем и поступает на его выход, а так как он соединён с входом третьего триггера, то и на его вход. В один момент следующий бит запоминается в первом триггере.

По окончании поступления четвертого тактового импульса в триггерах регистра будут записаны уровни бит, каковые последовательно находились на входе D0. Сейчас этими битами возможно воспользоваться, к примеру, для отображения на индикаторах.

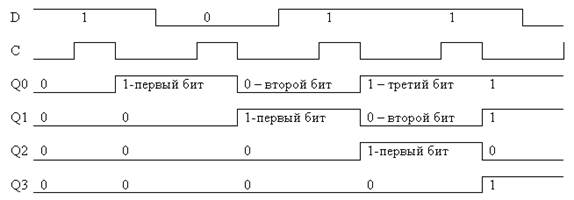

Пускай на вход регистра поступает сигнал, временная диаграмма которого изображена на рисунке 5, тогда состояние выходов этого регистра будет последовательно принимать значения, записанные в таблице 4.

Рисунок 5. Временная диаграмма работы сдвигового регистра.

На рисунке 5 вместе с логическими уровнями записываются значения бит, каковые передаются по соединительной линии либо присутствуют на выходах сдвигового регистра.

| № такта | ||||

| Q0 | ||||

| Q1 | X | |||

| Q2 | X | X | ||

| Q3 | X | X | X |

Универсальные регистры

Регистры сдвига делают в большинстве случаев как универсальные последовательно-параллельные микросхемы. Это связано с необходимостью записи в регистр параллельного бинарного кода при преобразовании параллельного кода в последовательный.

Переключение регистра из параллельного режима работы в последовательный и напротив осуществляется при помощи мультиплексора (коммутатора). Применение коммутатора разрешает входы триггеров регистра или подключать к внешним выводам микросхемы, или подключать к выходу прошлого триггера.

Напомню, что двухвходовый мультиплексор возможно реализовать при помощи логических элементов “2И-2Либо”. Элементы “И” наряду с этим трудятся в качестве электронных ключей, а элементы “Либо” объединяют их выходы.

Схема универсального регистра с применением коммутаторов на логических элементах “2И-2Либо” приведена на рисунке 6.

Рисунок 6. Схема универсального регистра.

В данной схеме для переключения регистра из последовательного режима работы в параллельный употребляется вывод V. Подача на данный вход единичного потенциала превращает схему в параллельный регистр. Наряду с этим на входы ключей, подключенных к информационным входам D, подаётся единичный потенциал. Это ведет к тому, что сигналы с входов параллельной записи данных поступают на входы логических элементов “Либо”, а на входы ключей, подключенных к выходам прошлых триггеров, подаются нулевые потенциалы. Другими словами на выходах этих ключей будут находиться нулевые потенциалы, и они не будут мешать работе.

Подача на вход V нулевого потенциала ведет к отключению входов параллельных данных от входов триггеров. Сигналы же с выхода прошлого триггера вольно проходит через верхние логические элементы “И” на вход последующего триггера, поскольку на его второй вход подаётся единичный потенциал.

Инверторы на входах V и C использованы для усиления входного сигнала по току. В следствии входной ток микросхемы будет равен не суммарному току четырёх логических элементов “И”, а входному току инвертора.

Условно-графическое изображение универсального регистра приведено на рисунке 7. Вход последовательного ввода данных на этом рисунке обозначен как DI и отделён от вторых групп входов чертой. Совершенно верно так же выделены в входы управления и отдельные группы V и синхронизации C.

Рисунок 7. Обозначение универсального регистра на принципиальных схемах.

Счётчики

Счётчики употребляются для построения таймеров либо для выборки руководств из ПЗУ в процессорах. Они смогут употребляться как делители частоты в управляемых генераторах частоты (синтезаторах). При применении в цепи ФАП счётчики смогут быть использованы для умножения частоты как в синтезаторах, так и в процессорах.