В задаче 3 рассматриваются следующие типовые КЦУ: преобразователи кодов, мультиплексоры, дешифраторы и шифраторы.

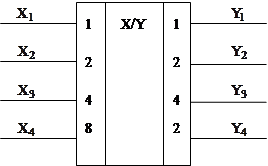

В вариантах 1,6 и 10 задачи 4 требуется синтезировать в базисе И-НЕ схемы преобразователей кодов. В книжках [1, С. 117-120] и [2, С. 188-190] приведены примеры синтеза преобразователя кода 8421 в код 2421 и обратно. Причем минимизация логических функций выполнена табличным способом посредством карт Вейча. Разглядим пример синтеза преобразователя кода 8421 в код 2421 при минимизации логических функций посредством карт Карно, каковые более эргономичны и нашли более широкое использование на практике. Условное графическое обозначение для того чтобы преобразователя кода представлено на рисунке 6.

Рисунок 6 – Условное графическое обозначение преобразователя кода 8421 в код 2421

Закон функционирования преобразователя кода представлен в таблице 7.

Таблица 7 – Таблица истинности преобразователя кода 8421 в код 2421

| Десятичное число | Код 8421 | Код 2421 | ||||||

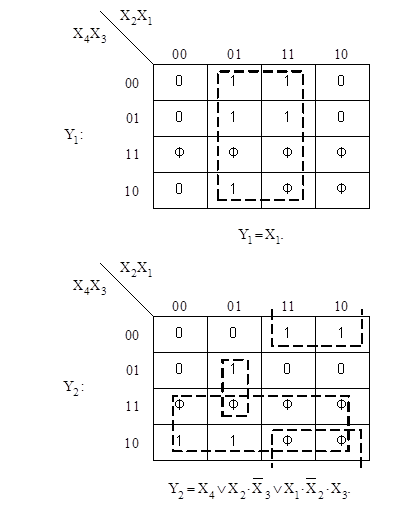

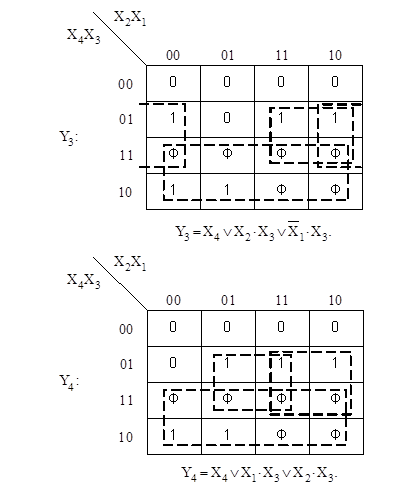

На основании таблицы истинности преобразователя кодов заполним карты Карно (рисунок 7) и запишем логические функции для выходов ,…, в МДНФ.

Рисунок 7 – Карты Карно для преобразователя кода 8421 в код 2421

Окончание рисунка 7

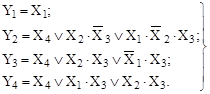

(3)

(3)

Преобразуем логические функции (3) в базис И-НЕ, применяя правило де Моргана.

| Для остальных выходов подобно: |

(4)

(4)

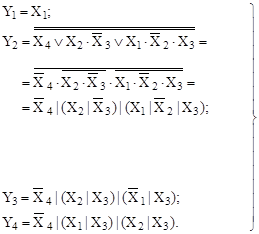

Логическая схема преобразователя кода 8421 в код 2421 в базисе И-НЕ, выстроенная по логическим функциям (4), представлена на рисунке 8.

Для проверки правильности функционирования логической схемы преобразователя кода проставим на выходах логических элементов значения сигналов для входного кодового слова 0011. Потому, что на выходах схемы устанавливается кодовое слово 0011, то преобразователь кода функционирует в соответствии с таблицей истинности.

направляться не забывать, что проверка правильности функционирования лишь по одному входному комплекту есть неполной.

Методика синтеза преобразователей кодов, заданных в вариантах 1, 6 и 10, подобна. Для составления таблицы истинности направляться применять эти таблицы 8.

Рисунок 8 – Логическая схема преобразователя кода 8421 в код 2421 в базисе И-НЕ

Таблица 8 – Бинарно-десятичные коды

| Десятичное число | Бинарно-десятичные коды | |||

| «с избытком 3» | ||||

| Примечание – Код «с избытком 3» довольно часто именуют кодом 8421+3 |

В вариантах 2 и 8 задачи 3 требуется синтезировать в базисе И-ИЛИ-НЕ схему мультиплексора на восемь каналов (мультиплексоры именуют коммутаторами каналов). Разглядим пример синтеза мультиплексора на четыре канала со стробированием. Условное назначение выводов и графическое обозначение мультиплексора представлено в [1, С. 123-125] и [3, С. 141-144]. Таблица истинности мультиплексора представлена в таблице 9.

Таблица 9 – Таблица истинности мультиплексора на четыре канала со стробированием

| Адресные входы | Стробирующий сигнал | Выход | |

| Q | |||

| X | X | ||

| Примечание – Знаком «X» обозначен произвольный уровень сигнала – 0 либо 1 |

Из таблицы истинности направляться, что при отсутствии стробирующего (разрешающего) сигнала ( =1) на выходе мультиплексора Q устанавливается нулевой сигнал независимо от кода на адресных входах , . При поступлении стробирующего сигнала ( =0) на выход мультиплексора Q передается сигнал с того информационного входа … , номер которого указан на адресных входах , .

На основании таблицы истинности мультиплексора запишем логическую функцию для выхода Q в идеальной дизъюнктивной обычной форме (СДНФ):

(5)

По логической функции (5) возможно выстроить логическую схему мультиплексора в базисе И, Либо, НЕ, но, более простой логическая схема мультиплексора будет в базисе И-ИЛИ-НЕ. Для преобразования логической функции (5) в базис И-ИЛИ-НЕ направляться проинвертировать левую и правую части равенства:

(6)

Из логической функции (6) направляться, что в базисе И-ИЛИ-НЕ мультиплексор будет иметь инверсный выход, исходя из этого для получения прямого выхода к его выходу направляться подключить инвертор.

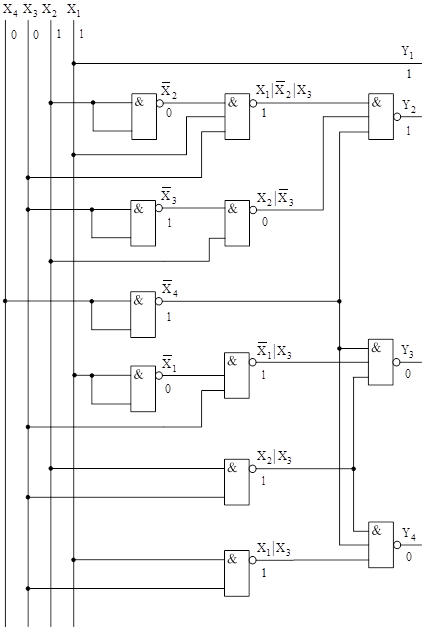

Логическая схема мультиплексора в базисе И-ИЛИ-НЕ, выстроенная по логической функции (6), представлена на рисунке 9.

Для проверки правильности функционирования логической схемы мультиплексора проставим значения сигналов для адресного кода 11. Потому, что на выход схемы Q передается сигнал со входа D3, то мультиплексор функционирует в соответствии с таблицей истинности.

Синтез мультиплексора, заданного в вариантах 2 и 8, направляться делать по приведенной выше методике.

В вариантах 3, 5 и 9 задачи 3 требуется синтезировать схему дешифратора в базисе И-НЕ со стробированием, т.е. с разрешающим входом .

Рисунок 9 – Логическая схема мультиплексора в базисе И-ИЛИ-НЕ

Условное графическое обозначение дешифратора с инверсными выходами представлено на рисунке 10.

Рисунок 10 – Условное графическое обозначение дешифратора кода 8421 на десять выходов в базисе И-НЕ со стробированием

В дешифраторах с инверсными выходами активным уровнем сигнала на выходах есть уровень логического нуля.

Таблица истинности дешифратора представлена в таблице 10.

Таблица 10 – Таблица истинности дешифратора кода 8421 на десять выходов со стробированием

| Входной код 8421 | Строб (разрешение) | Выходные сигналы | ||||||||||||

| X | X | X | X | |||||||||||

Из таблицы истинности направляться, что дешифратор преобразует входной код в сигнал активного уровня на одном из выходов, в случае, если на стробирующем входе деятельный уровень сигнала ( = 0). В другом случае на всех выходах дешифратора устанавливаются пассивные уровни сигнала (единичные).

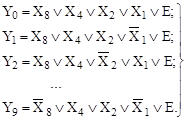

Согласно данным таблицы 10 запишем логические функции для выходов дешифратора в СКНФ:

(7)

(7)

Преобразуем логические функции (7) в базис И-НЕ, применяя закон двойного отрицания и правило де Моргана:

(8)

(8)

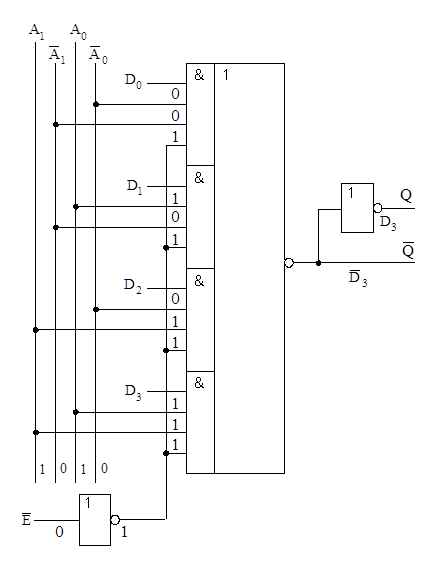

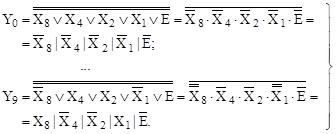

Логическая схема дешифратора в базисе И-НЕ, выстроенная по логическим функциям (8), представлена на рисунке 11.

направляться не забывать, что в дешифраторах с прямыми выходами активным уровнем сигнала на выходах есть уровень логической единицы и логические функции направляться записывать в СДНФ.

Потому, что на рисунке 11 представлена упрощенная логическая схема дешифратора, то диагностику правильности ее функционирования выполним не для четвертой, а для десятой строки таблицы истинности. Так как деятельный уровень сигнала устанавливается на выходе то схема дешифратора функционирует в соответствии с таблицей истинности.

Рисунок 11 – Логическая схема дешифратора кода 8421 на десять выходов в базисе И-НЕ со стробированием

Синтез логической схемы дешифратора, заданного в вариантах 3, 5 и 9, направляться делать по приведенной выше методике. При составлении таблицы истинности заданного дешифратора употребляются эти таблицы 8. Логические функции записываются для всех выходов дешифратора, и строится полная логическая схема.

В вариантах 4 и 7 задачи 3 требуется синтезировать схему шифратора. В книжках [1, С. 110-112] и [2, С. 181-184] продемонстрирован пример синтеза бинарного шифратора десятичных цифр от 0 до 9 в код 8421 без стробирования. Разглядим пример синтеза шифратора десятичных цифр от 0 до 9 в код 8421 со стробированием.

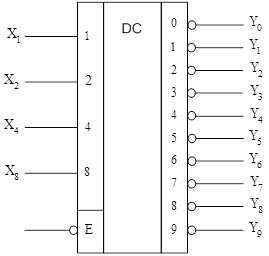

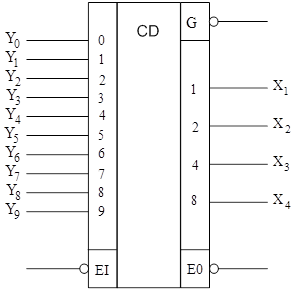

Условное графическое обозначение шифратора для преобразования десятичных цифр от 0 до 9 в код 8421 с разрешающим (стробирующим) входом представлено на рисунке 12.

Рисунок 12 – Условное графическое обозначение шифратора для преобразования десятичных цифр от 0 до 9 в код 8421

Сигналы, соответствующие десятичным цифрам, подаются на входы , ,…,

Нулевое значение сигнала на разрешающем (стробирующем) входе разрешает работу данного шифратора. Нулевое значение сигнала на выходе отмечает наличие возбужденного входа у данного шифратора.

Дабы выделить обстановку, в то время, когда отсутствуют возбужденные входы, в данном шифраторе имеется дополнительный выход (разрешение по выходу). Нулевое значение сигнала на выходе вырабатывается при отсутствии возбужденных входов у данного шифратора для разрешения работы следующего (младшего) шифратора при наращивании выходов и числа входов.

На выходах – формируется выходное кодовое слово.

Таблица истинности, обрисовывающая функционирование данного шифратора, представлена в таблице 11.

Таблица 11 – Таблица истинности шифратора для преобразования десятичных цифр от 0 до 9 в код 8421

| Входные сигналы | Выходные сигналы | |||||||||||||||

| X | X | X | X | X | X | X | X | X | X | |||||||

Как видно из таблицы истинности, все перечисленные выше сигналы на выходах шифратора формируются при наличии активного уровня сигнала на входе разрешения ( = 0). При пассивном уровне сигнала на входе разрешения ( = 1) независимо от состояния информационных входов шифратора на информационных выходах формируется пассивные уровни 0000 и кодовое слово сигналов на выходах и .

При отсутствии возбужденных входов (вторая строчок в таблице истинности) на выходе формируется деятельный уровень сигнала ( = 0).

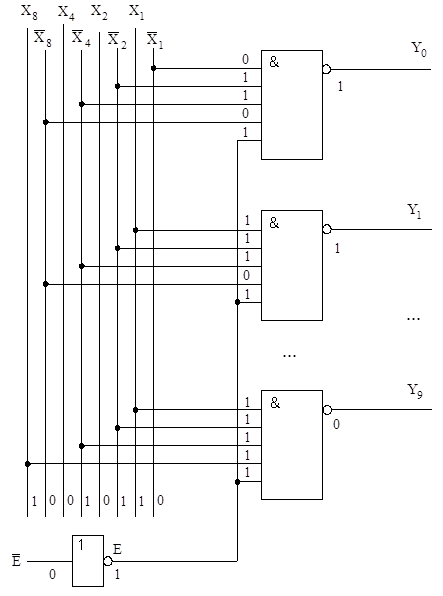

Согласно данным таблицы 11 запишем логические функции для информационных выходов шифратора. Любая из них воображает дизъюнкцию входных доводов (i = 0, 1, … , 9), для которых значение функции равняется 1.

(9)

(9)

Из таблицы истинности разумеется, что логическая функция для выхода есть инверсией логической функции для выхода .

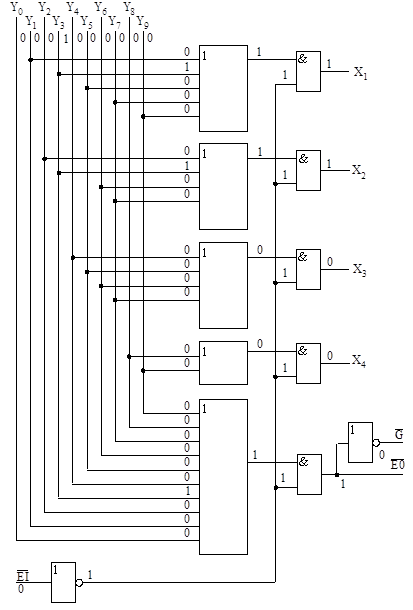

Логическая схема шифратора в базисе И, Либо НЕ, выстроенная по логическим функциям (9), представлена на рисунке 13.

Для проверки правильности функционирования логической схемы шифратора подадим на ее входы сигналы, соответствующие четвертой строке таблицы истинности ( = 1). Так как на выходах устанавливается кодовое слово 0011, конечно = 0, = 1, то логическая схема шифратора функционирует в соответствии с таблицей истинности.

Синтез логической схемы шифратора, заданного в вариантах 4 и 7, направляться делать по приведенной выше методике. При составлении таблицы истинности в качестве выходного кода , , , применять эти таблицы 8.

Рисунок 13 – Логическая схема шифратора для преобразования десятичных цифр от 0 до 9 в код 8421 в базисе И, Либо, НЕ со стробированием

Контрольная задача 4

Синтезировать цифровой автомат с двумя состояниями, выбрав собственный вариант из таблицы 10.

Таблица 10 — Варианты цифровых автоматов для синтеза